and and the second seco

The Connection Machine System

# **NI Systems Programming**

Version 7.1 October 1992

Thinking Machines Corporation Cambridge, Massachusetts

#### \*\*\*\*\*\*\*\*

The information in this document is subject to change without notice and should not be construed as a commitment by Thinking Machines Corporation. Thinking Machines Corporation reserves the right to make changes to any products described herein to improve functioning or design. Although the information in this document has been reviewed and is believed to be reliable, Thinking Machines Corporation does not assume responsibility or liability for any errors that may appear in this document. Thinking Machines Corporation does not assume not assume any liability arising from the application or use of any information or product described herein.

\*\*\*\*\*\*\*\*

Connection Machine<sup>®</sup> is a registered trademark of Thinking Machines Corporation. CM, CM-2, CM-5, CMOST and NI are trademarks of Thinking Machines Corporation. Thinking Machines<sup>®</sup> is a trademark of Thinking Machines Corporation. SPARC and SPARCstation are trademarks of SPARC International, Inc. Sun, Sun-4, and Sun Workstation are trademarks of Sun Microsystems, Inc. UNIX is a registered trademark of UNIX System Laboratories, Inc. The X Window System is a trademark of the Massachusetts Institute of Technology.

Copyright © 1992 by Thinking Machines Corporation. All rights reserved.

Thinking Machines Corporation 245 First Street Cambridge, Massachusetts 02142–1264 (617) 234–1000

# Contents

|           | _                                                                 | :          |

|-----------|-------------------------------------------------------------------|------------|

|           | s                                                                 | xi<br>viii |

|           | port                                                              |            |

| Chapter 1 | The Network Interface Chip                                        | 1          |

| 1.1       | The CM-5 System: Nodes and Networks                               | 1          |

|           | 1.1.1 The CM-5 Networks                                           | 2          |

|           | 1.1.2 Processing Nodes                                            | 3          |

|           | 1.1.3 Partitions and Partition Managers                           | 3          |

|           | 1.1.4 Programming Models                                          | 4          |

| 1.2       | The NI Chip                                                       | 5          |

| 1.3       | The NI Registers                                                  | 6          |

|           | 1.3.1 NI Register Types                                           | 7          |

|           | 1.3.2 NI Register and Field Names                                 | 7          |

|           | 1.3.3 NI Register and Field Programming Constants                 | 8          |

|           | 1.3.4 For the Curious: The NI Base Address — Physical and Virtual | 10         |

| 1.4       | Interrupts                                                        | 11         |

| 1.5       | NI Reset                                                          | 12         |

| Chapter 2 | A Generic Network Interface                                       | 13         |

| 2.1       | Network Interface Registers                                       | 13         |

| 2.2       | Network Messages                                                  | 14         |

|           | 2.2.1 Performance Note — Using Doubleword Operations              | 15         |

| 2.3       | Sending a Message                                                 | 15         |

|           | 2.3.1 Message Discarding                                          | 16         |

|           | 2.3.2 Auxiliary Information                                       | 16         |

|           | 2.3.3 Calculating ni_interface_send_first Addresses               | 17         |

|           | Send First Address Constants                                      | 17         |

| 2.4       | Receiving a Message                                               | 18         |

|           | 2.4.1 Detecting Arrival of a Message                              | 18         |

|           | 2.4.2 Simulating the Arrival of a Message                         | 19         |

.

(

Ģ

# Chapter 2 A Generic Network Interface cont'd

| 2.5                             | The Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19                                                                         |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|                                 | 2.5.1 The "Send OK" Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19                                                                         |

|                                 | 2.5.2 The "Send Space" Field and "Send Empty" Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                                                                         |

|                                 | 2.5.3 The "Receive OK" Flag and "Receive Length" Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                                         |

| 2.6                             | Abstaining from an Interface — The Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21                                                                         |

|                                 | 2.6.1 Effect of Abstain Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21                                                                         |

|                                 | 2.6.2 Combine Interface Abstain Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21                                                                         |

|                                 | 2.6.3 Use the Abstain Flags Safely                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                                         |

|                                 | 2.6.4 Being a Good Neighbor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22                                                                         |

| 2.7                             | The Private Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23                                                                         |

|                                 | 2.7.1 Message Receipt Interrupts — The Rec Interrupt Enable Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                                         |

|                                 | 2.7.2 Clearing the Interface's Send FIFO — The Lock Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24                                                                         |

|                                 | 2.7.3 Grabbing the Receive FIFO Registers — The Rec Stop Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24                                                                         |

|                                 | 2.7.4 Blocking Unsent Broadcast Messages — The Send Stop Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25                                                                         |

|                                 | 2.7.5 Detecting a Full Receive FIFO — The Receive Full flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                                                         |

| 2.8                             | Using a Generic Network Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                                         |

| 2.9                             | From the Generic to the Specific                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26                                                                         |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

| Chanter 3                       | The Data Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77                                                                         |

| Chapter 3                       | The Data Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27                                                                         |

| <b>Chapter 3</b> 3.1            | The Data Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27<br>28                                                                   |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

| 3.1                             | The Data Network Register Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28                                                                         |

| 3.1<br>3.2                      | The Data Network Register Interfaces      Data Network Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28<br>30                                                                   |

| 3.1<br>3.2<br>3.3               | The Data Network Register Interfaces         Data Network Messages         Data Network Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28<br>30<br>30                                                             |

| 3.1<br>3.2<br>3.3<br>3.4        | The Data Network Register Interfaces         Data Network Messages         Data Network Addressing         Sending and Receiving Messages                                                                                                                                                                                                                                                                                                                                                                                                                            | 28<br>30<br>30<br>32                                                       |

| 3.1<br>3.2<br>3.3<br>3.4        | The Data Network Register Interfaces         Data Network Messages         Data Network Addressing         Sending and Receiving Messages         The Status Register                                                                                                                                                                                                                                                                                                                                                                                                | 28<br>30<br>30<br>32<br>34                                                 |

| 3.1<br>3.2<br>3.3<br>3.4        | The Data Network Register Interfaces         Data Network Messages         Data Network Addressing         Sending and Receiving Messages         The Status Register         3.5.1         Message Tags                                                                                                                                                                                                                                                                                                                                                             | 28<br>30<br>30<br>32<br>34<br>34                                           |

| 3.1<br>3.2<br>3.3<br>3.4        | The Data Network Register Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28<br>30<br>30<br>32<br>34<br>34<br>35                                     |

| 3.1<br>3.2<br>3.3<br>3.4        | The Data Network Register Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28<br>30<br>30<br>32<br>34<br>34<br>35<br>35                               |

| 3.1<br>3.2<br>3.3<br>3.4        | The Data Network Register Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28<br>30<br>32<br>34<br>34<br>35<br>35<br>36                               |

| 3.1<br>3.2<br>3.3<br>3.4        | The Data Network Register Interfaces         Data Network Messages         Data Network Addressing         Sending and Receiving Messages         Sending and Receiving Messages         The Status Register         3.5.1 Message Tags         User/Supervisor Tag Reservation         Tag Fields and Interrupts         Tag Fields and the Message-Counting Registers         Message Count Disabling         Negative Message Count Interrupts         3.5.2 IMPORTANT — Check the Tag before Receiving a Message                                                 | 28<br>30<br>32<br>34<br>35<br>35<br>36<br>36<br>37<br>37                   |

| 3.1<br>3.2<br>3.3<br>3.4        | The Data Network Register Interfaces         Data Network Messages         Data Network Addressing         Sending and Receiving Messages         Sending and Receiving Messages         The Status Register         3.5.1 Message Tags         User/Supervisor Tag Reservation         Tag Fields and Interrupts         Tag Fields and the Message-Counting Registers         Message Count Disabling         Negative Message Count Interrupts         3.5.2 IMPORTANT — Check the Tag before Receiving a Message         3.5.3 The Send and Receive State Fields | 28<br>30<br>32<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>38             |

| 3.1<br>3.2<br>3.3<br>3.4        | The Data Network Register Interfaces         Data Network Messages         Data Network Addressing         Sending and Receiving Messages         Sending and Receiving Messages         The Status Register         3.5.1 Message Tags         User/Supervisor Tag Reservation         Tag Fields and Interrupts         Tag Fields and the Message-Counting Registers         Message Count Disabling         Negative Message Count Interrupts         3.5.2 IMPORTANT — Check the Tag before Receiving a Message                                                 | 28<br>30<br>32<br>34<br>35<br>35<br>36<br>36<br>37<br>37                   |

| 3.1<br>3.2<br>3.3<br>3.4        | The Data Network Register Interfaces<br>Data Network Messages .<br>Data Network Addressing<br>Sending and Receiving Messages .<br>The Status Register .<br>3.5.1 Message Tags .<br>User/Supervisor Tag Reservation .<br>Tag Fields and Interrupts .<br>Tag Fields and the Message-Counting Registers .<br>Message Count Disabling .<br>Negative Message Count Interrupts .<br>3.5.2 IMPORTANT — Check the Tag before Receiving a Message<br>3.5.3 The Send and Receive State Fields<br>3.5.4 The Network-Done Flag                                                   | 28<br>30<br>32<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>38             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | The Data Network Register Interfaces         Data Network Messages         Data Network Addressing         Sending and Receiving Messages         The Status Register         3.5.1 Message Tags         User/Supervisor Tag Reservation         Tag Fields and Interrupts         Tag Fields and the Message-Counting Registers         Message Count Disabling         Negative Message Count Interrupts         3.5.2 IMPORTANT — Check the Tag before Receiving a Message         3.5.3 The Send and Receive State Fields         3.5.4 The Network-Done Flag    | 28<br>30<br>32<br>34<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>38<br>39 |

)

| Chapter 4 | The Control Network     |                                                       |           |

|-----------|-------------------------|-------------------------------------------------------|-----------|

| 4.1       | The Broadcast Interface |                                                       |           |

|           | 4.1.1                   | Broadcast Register Interfaces                         | 44        |

|           | 4.1.2                   | Broadcast Messages                                    | 45        |

|           | 4.1.3                   | Sending Broadcast Messages                            | 46        |

|           | 4.1.4                   | Receiving Broadcast Messages                          | 47        |

|           | 4.1.5                   | The Broadcast Status Register                         | 47        |

|           |                         | How to Interpret the Value of the "Length Left" Field | 48        |

|           | 4.1.6                   | Abstaining from the Broadcast Interface               | 48        |

|           | 4.1.7                   | The Broadcast Private Register                        | 48        |

|           |                         | The Send Enable Flag                                  | <b>49</b> |

| 4.2       | The Com                 | bine Interface                                        | 49        |

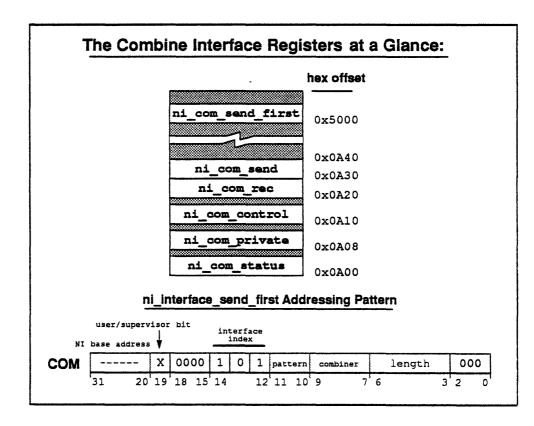

|           | 4.2.1                   | The Combine Register Interface                        | 50        |

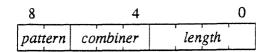

|           | 4.2.2                   | Combine Messages                                      | 51        |

|           | 4.2.3                   | Sending Combine Messages                              | 51        |

|           | 4.2.4                   | Receiving Combine Message                             | 53        |

|           | 4.2.5                   | The Combine Status Register                           | 53        |

|           | 4.2.6                   | Scanning (Parallel Prefix) and Reduction Operations   | 54        |

|           |                         | Scanning with Segments                                | 54        |

|           |                         | Addition Scan Overflow                                | 55        |

|           | 4.2.7                   | Network-Done Messages                                 | 55        |

|           |                         | How Network-Done Works                                | 56        |

|           |                         | And Why You Should Care                               | 57        |

|           | 4.2.8                   | Abstaining from the Combine Interface                 | 58        |

|           |                         | The Reduction Receive Abstain Flag                    | 58        |

|           | 4.2.9                   | The Combine Private Register                          | 59        |

|           |                         | Empty Receive FIFO Interrupt                          | 59        |

|           |                         | Clearing the Combine Send FIFO                        | 59        |

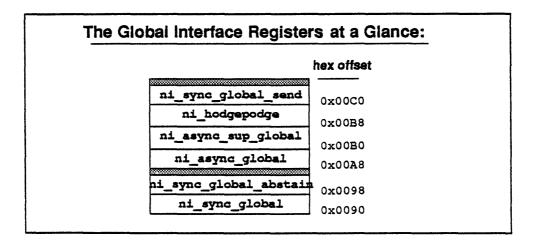

| 4.3       | The Glob                | al Interface                                          | 61        |

|           | 4.3.1                   | The Three Global Register Interfaces                  | 62        |

|           | 4.3.2                   | The Synchronous Global Interface                      | 62        |

|           |                         | Sending and Receiving Messages                        | 63        |

|           |                         | Abstaining from Synchronous Global Messages           | 63        |

|           |                         | Synchronous Global Receive Interrupt                  | 63        |

|           | 4.3.3                   | The Asynchronous Global Interface                     | 64        |

|           |                         | Sending and Receiving Messages                        | 64        |

|           |                         | Asynchronous Global Receive Interrupt                 | 65        |

|           | 4.3.4                   | The Supervisor Asynchronous Global Interface          | 65        |

|           |                         | Sending and Receiving Messages                        | 65        |

|           |                         | Supervisor Asynchronous Global Receive Interrupt      | 65        |

| <ul> <li>5.1 Interrupt Classes</li></ul>                                                                                                                                                                                                                                                                                                                                                                              |           | 67<br>70<br>70<br>72<br>72 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------|

| 5.2.1       Red Interrupts         5.2.2       Orange Interrupts         5.2.3       Yellow Interrupts         5.2.4       Green Interrupts         5.3       The Interrupt Cause and Clear Registers         5.4       Interrupt Levels         5.5       Broadcast Interrupts         5.6       Recovering from Interrupts         5.6       Recovering from Interrupts         6.1       The "Hodgepodge" Register |           | 70<br>72<br>72             |

| <ul> <li>5.4 Interrupt Levels</li></ul>                                                                                                                                                                                                                                                                                                                                                                               | -         | 72                         |

| <ul> <li>5.5 Broadcast Interrupts</li> <li>5.6 Recovering from Interrupts</li> <li>Chapter 6 Other NI Interfaces and Features</li> <li>6.1 The "Hodgepodge" Register</li> </ul>                                                                                                                                                                                                                                       |           | 73                         |

| <ul> <li>5.6 Recovering from Interrupts</li> <li>Chapter 6 Other NI Interfaces and Features</li> <li>6.1 The "Hodgepodge" Register</li> </ul>                                                                                                                                                                                                                                                                         | ••••      | 74                         |

| Chapter 6 Other NI Interfaces and Features         6.1 The "Hodgepodge" Register                                                                                                                                                                                                                                                                                                                                      | ••••      | 75                         |

| 6.1 The "Hodgepodge" Register                                                                                                                                                                                                                                                                                                                                                                                         | • • • • • | 76                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                       |           | 77                         |

| 6.2 Node Address Registers                                                                                                                                                                                                                                                                                                                                                                                            |           | 77                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                       | •••••     | 78                         |

| 6.3 NI Chunk Table and Address Translation                                                                                                                                                                                                                                                                                                                                                                            |           | 78                         |

| 6.4 Combine Interface Flush                                                                                                                                                                                                                                                                                                                                                                                           | 8         | 82                         |

| 6.5 The NI Timer                                                                                                                                                                                                                                                                                                                                                                                                      | 8         | 83                         |

| 6.6 The Bad Address Register                                                                                                                                                                                                                                                                                                                                                                                          | 8         | 83                         |

| 6.7 NI Partition Configuration                                                                                                                                                                                                                                                                                                                                                                                        | 8         | 84                         |

| 6.8 Disabling the Control Network                                                                                                                                                                                                                                                                                                                                                                                     | 8         | 85                         |

| 6.9 NI Serial Number                                                                                                                                                                                                                                                                                                                                                                                                  | 8         | 86                         |

| 6.10 NI Reset                                                                                                                                                                                                                                                                                                                                                                                                         | · 8       | 86                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                            |

| Chapter 7 NI Programming Issues                                                                                                                                                                                                                                                                                                                                                                                       | 8         | 89                         |

| 7.1 The Partition Manager                                                                                                                                                                                                                                                                                                                                                                                             | 8         | 89                         |

| 7.1.1 Sending Messages between the PM and the Nodes                                                                                                                                                                                                                                                                                                                                                                   |           | 90                         |

| 7.1.2 For the Curious: Using the Data Network                                                                                                                                                                                                                                                                                                                                                                         |           | 90                         |

| 7.2 Performance Hints                                                                                                                                                                                                                                                                                                                                                                                                 |           | 91                         |

| 7.2.1 NI Register Operation Times                                                                                                                                                                                                                                                                                                                                                                                     |           | 91<br>01                   |

| <ul><li>7.2.2 Reading and Writing Registers with Doubleword Values</li><li>7.2.3 Use Message Discarding for Efficiency</li></ul>                                                                                                                                                                                                                                                                                      |           |                            |

| 7.2.4 Set the Abstain Flags Once and Forget Them                                                                                                                                                                                                                                                                                                                                                                      |           | 91<br>92                   |

ſ

# Chapter 7 NI Programming Issues cont'd

| 7.3 | Potential | Programming Traps and Snares                              | 93 |

|-----|-----------|-----------------------------------------------------------|----|

|     | 7.3.1     | Pay Attention to Data Network Addresses                   | 93 |

|     | 7.3.2     | Check the Tag before Retrieving a Data Network Message    | 93 |

|     | 7.3.3     | Make Sure Doubleword Data Is Doubleword Aligned           | 94 |

|     | 7.3.4     | Order Is Important in Combine Messages                    | 94 |

|     | 7.3.5     | Restriction on Network-Done Operations for Rev A NI Chips | 94 |

|     | 7.3.6     | Simulating Receipt of Messages                            | 95 |

|     | 7.3.7     | Broadcast Enabling                                        | 96 |

|     | 7.3.8     | Broadcast and Combine Interface Conflicts                 | 96 |

|     | 7.3.9     | Be Careful When Altering Abstain Flags                    | 96 |

|     |           |                                                           |    |

# Appendixes

| Appendix A | NI Memory Map 99                                                                                    |

|------------|-----------------------------------------------------------------------------------------------------|

| Appendix B | NI Registers, Fields, and Constants 103                                                             |

| B.1        | NI Registers103B.1.1Global and System Registers104B.1.2Network Interface Registers105               |

| B.2        | NI Message Length Limit Constants 106                                                               |

| B.3        | Send First Register Addresses 107                                                                   |

| B.4        | NI Fields                                                                                           |

|            | The ni_dr_status Register 110                                                                       |

|            | The ni_dr_private Register                                                                          |

|            | B.4.2 Left Data Network Interface (LDR) Fields                                                      |

|            | The ni_ldr_private Register                                                                         |

|            | B.4.3 Right Data Network Interface (RDR) Fields 112                                                 |

|            | The ni_rdr_status Register 112                                                                      |

|            | The ni_rdr_private Register       112         B.4.4       Broadcast Interface (BC) Fields       112 |

|            | B.4.4 Broadcast Interface (BC) Fields                                                               |

|            | The ni_bc_private Register                                                                          |

|            | The ni_bc_control Register                                                                          |

| B.4        | NI Fields, | cont.                                                  |

|------------|------------|--------------------------------------------------------|

|            | B.4.5      | Supervisor Broadcast Interface (SBC) Fields            |

|            |            | The ni_sbc_status Register                             |

|            |            | The ni_sbc_private Register                            |

|            |            | The ni_sbc_control Register 114                        |

|            | B.4.6      | Combine Interface (COM) Fields                         |

|            |            | The ni_com_status Register 114                         |

|            |            | The ni_com_private Register 114                        |

|            |            | The ni_com_control Register 115                        |

|            | B.4.7      | Global Interface Fields 115                            |

|            |            | The ni_sync_global Register 115                        |

|            |            | The ni_async_global Register 115                       |

|            |            | The ni_async_sup_global Register 115                   |

|            | B.4.8      | Interrupt Register Fields 116                          |

|            |            | The ni_interrupt_cause Register 116                    |

|            |            | The ni_interrupt_cause_green Register 116              |

|            |            | The ni_interrupt_clear Register 117                    |

|            |            | The ni_interrupt_clear_green Register 117              |

|            | B.4.9      | Other Register Fields and Constants 118                |

|            |            | The ni_interrupt_level Register 118                    |

|            |            | The ni_hodgepodge Register 118                         |

|            |            | The ni_bad_address Register 118                        |

|            |            |                                                        |

| Appendix C | Predefir   | ned Low-Level NI Constants                             |

| Appendix C |            |                                                        |

|            |            |                                                        |

| Appendix D | NI Inter   | rupts 127                                              |

| D.1        | Red Interr | rupts                                                  |

|            | D.1.1      | Internal Fault Red Interrupt 128                       |

|            | D.1.2      | CN Checksum Error, DR Checksum Error Red Interrupt 128 |

|            | D.1.3      | CN Hard Error Red Interrupt 129                        |

|            | D.1.4      | MC Error, CMU Error Red Interrupt 129                  |

|            | D.1.5      | BC Interrupt Red Red Interrupt 130                     |

| D.2 · Orange In | terrupts                               | 130 |

|-----------------|----------------------------------------|-----|

| D.2.1           | Timer Interrupt Orange Interrupt 1     | 130 |

| D.2.2           | BC Interrupt Orange Orange Interrupt 1 | 131 |

. . . . . . . . .

Ŕ

# Appendix D NI Interrupts cont'd

| D.3        | Yellow Interrupts 131                                              |

|------------|--------------------------------------------------------------------|

|            | D.3.1 BC Interrupt Yellow                                          |

|            | D.3.2 COM Abstain Changed Yellow Interrupt 132                     |

|            | D.3.3 DR Count Negative                                            |

|            | D.3.4 BC or COM Collision Yellow Interrupt 133                     |

|            | D.3.5 Bad Relative Address Yellow Interrupt 133                    |

| D.4        | Green Interrupts                                                   |

|            | D.4.1 BC Interrupt Green Green Interrupt 134                       |

|            | D.4.2 DR Receive Tag Green Interrupt 134                           |

|            | D.4.3 DR Receive All Fall Down Green Interrupt 135                 |

|            | D.4.4 Interface (DR, BC, COM, etc.) Receive OK Green Interrupt 135 |

|            | D.4.5 Global Rec (Sync, Global, or Supervisor) Green Interrupt 136 |

|            | D.4.6 Com Receive Empty Green Interrupt 136                        |

|            | D.4.7 Scan Overflow Green Interrupt 137                            |

| D.5        | Bus Errors                                                         |

|            | D.5.1 Bad Memory Access Bus Error 137                              |

|            |                                                                    |

| Appendix E | NI Programming Examples 141                                        |

| E.1        | Reading and Writing Registers 141                                  |

| E.2        | Reading and Writing Subfields 142                                  |

| E.3        | Constructing Send-First Addresses                                  |

|            | Data Network Send-First Macros                                     |

|            | Broadcast Interface Send-First Macros 144                          |

|            | Combine Interface Send-First Macros 144                            |

|            |                                                                    |

| Annendix F | CMNA Header Files                                                  |

#### Indexes

| Programming Tools I | ndex | • • • • • • • • • • • • • • • • • • • • | 151 |

|---------------------|------|-----------------------------------------|-----|

| Concepts Index      |      |                                         | 159 |

.

• (

# **List of Figures**

)

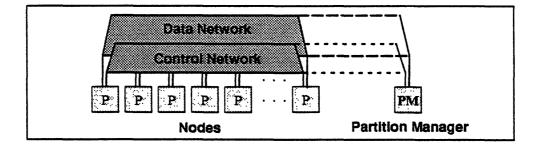

| Figure 1.  | CM-5 processing nodes linked by Data Network and Control Network       | 1   |

|------------|------------------------------------------------------------------------|-----|

| Figure 2.  | The components of a typical processing node.                           | 3   |

| Figure 3.  | A partition of nodes and its partition manager.                        | 3   |

| Figure 4.  | NI provides access to features of the Data Network and Control Network | 5   |

| Figure 5.  | The NI registers are mapped into user and supervisor memory areas      | 6   |

| Figure 6.  | Sample virtual memory maps showing location of NI memory region        | 10  |

| Figure 7.  | NI registers associated with each network.                             | 14  |

| Figure 8.  | The three interfaces of the Data Network: DR, LDR, and RDR             | 27  |

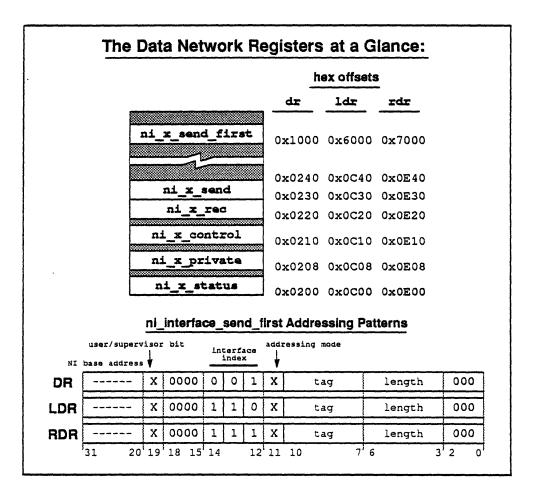

| Figure 9.  | NI registers associated with each of the Data Network interfaces.      | 29  |

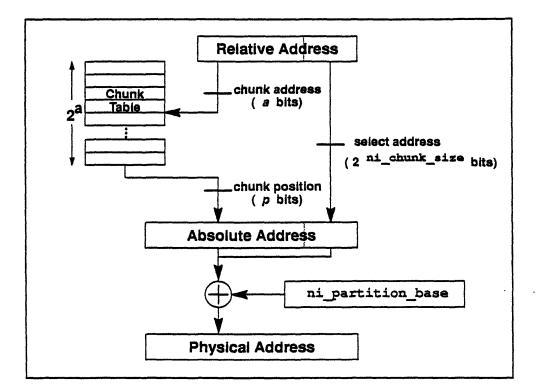

| Figure 10. | Relative addressing of nodes in a partition.                           | 31  |

| Figure 11. | The three interfaces of the Control Network: BC, COM, and Global       | 43  |

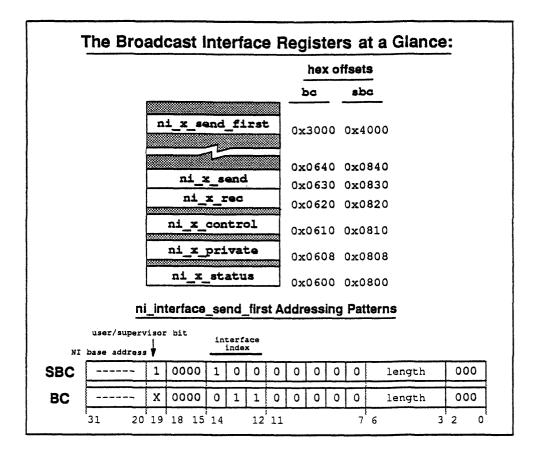

| Figure 12. | NI registers associated with each of the broadcast interfaces.         | 45  |

| Figure 13. | NI registers associated with the combine interface.                    | 50  |

| Figure 14. | NI registers associated with the global interface.                     | 61  |

| Figure 15. | The possible pathways for colored interrupts.                          | 70  |

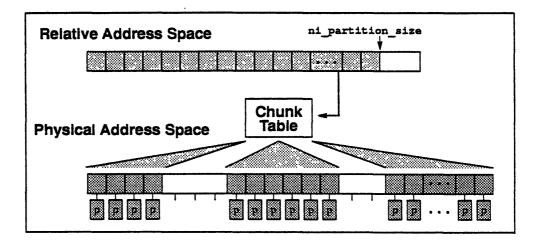

| Figure 16. | Translation from relative addresses to physical addresses              | 79  |

| Figure 17. | The chunk table is used to map contiguous relative addresses           |     |

|            | onto discontiguous physical addresses.                                 | 80  |

| Figure 18. | The partition manager stands apart from the partition it manages       | 89  |

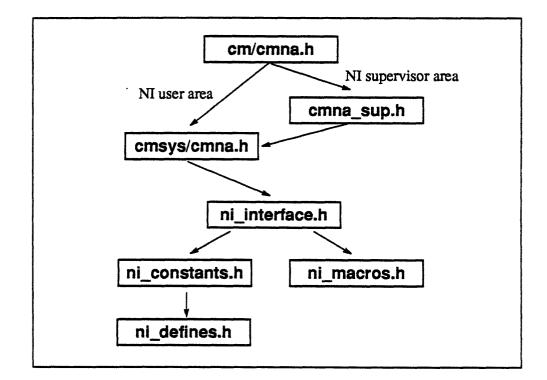

| Figure 19. | Relationship between CMNA and NI header files.                         | 146 |

.

Ę

.

# **About This Manual**

#### **Objectives of This Manual**

This manual describes in detail the design, features, and proper use of the Network Interface (NI) chip of the Connection Machine CM-5 system, at a level sufficient for low-level CM-5 coders to make full use of the NI's features.

This manual describes the NI from a system programmer's point of view. It discusses user and supervisor features of the NI, and provides enough detail to allow a knowledgeable CM-5 programmer to write code that manipulates the NI. The appendixes of this document include C code examples and references to on-line sources of sample NI code.

#### **Intended Audience**

This manual is intended for use by knowledgeable CM-5 programmers. While it contains some overview information, this document is a reference manual, not a tutorial. This manual should be used in conjunction with other programming guides and with assistance from Thinking Machines Corporation representatives.

For examples of NI programs written and compiled in C code, refer to the existing *Programming the NI* manual.

#### **Revision Information**

This manual is new as of Version 7.1. It is based on the existing *Programming* the NI manual, but includes additional supervisor information that was excluded from *Programming the NI*.

#### **Organization of This Manual**

#### Chapter 1 The Network Interface Chip An overview of the NI chip's purpose in the CM-5 hardware, and a description of the important features of the chip.

#### Chapter 2 A Generic Network Interface A description of common features found in most of the NI network interfaces.

#### Chapter 3 The Data Network The registers and features of the three Data Network interfaces.

#### Chapter 4 The Control Network The registers and features of the three Control Network interfaces (broadcast, combine, and global).

#### Chapter 5 NI Interrupts

A description of the various interrupt classes of the NI, and of the mechanisms used to detect and signal NI interrupts.

#### Chapter 6 Other NI Interfaces and Features A description of NI registers and features not covered by the preceding chapters.

#### Chapter 7 NI Programming Issues A summary of important programming and performance considerations that you should keep in mind while writing code that manipulates the NI.

#### Appendix A NI Memory Map A two-sided memory and register map, showing the arrangement of the NI's registers and register subfields.

#### Appendix B NI Registers, Fields, and Constants

A summary of the registers and fields of the NI chip and of the programming constants that can be used to locate them.

- 13 A - A BY SEA OF STATE AND A

xv

| Appendix C | Predefined Low-level Constants<br>A list of all low-level programming constants defined by the<br>files cmsys/ni_constants.h and cmsys/ni_defines.h,<br>with the symbols grouped by register and field. |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix D | NI Interrupts<br>A description of each of the possible NI interrupts, including<br>what they indicate and how to recover from them.                                                                     |

| Appendix E | NI Programming Examples<br>A set of simple C code examples of routines that read and write<br>NI registers and perform other useful functions.                                                          |

| Appendix F | CMNA Header Files<br>Describes the content and relationship between the various<br>header files that define the CM Network Accessor interface.                                                          |

#### **Related Documents**

These documents are part of the Connection Machine documentation set:

- Connection Machine CM-5 Technical Summary, January 1992

- Programming the NI, March 1992

-----

- m -

(

his

### **Notation Conventions**

The table below displays the notation conventions observed in this manual.

| Convention                                      | Meaning                                                                                                                                                                                                                                                                    |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bold typewriter                                 | UNIX and CM System Software commands, com-<br>mand options, and filenames, when they appear<br>embedded in text. Also, syntax statements and pro-<br>gramming language elements, such as keywords,<br>operators, and function names, when they appear<br>embedded in text. |

| italics                                         | Argument names and placeholders in function and command formats.                                                                                                                                                                                                           |

| typewriter                                      | Code examples and code fragments.                                                                                                                                                                                                                                          |

| <pre>% bold typewriter regular typewriter</pre> | In interactive examples, user input is shown in <b>bold typewriter</b> and system output is shown in regular typewriter font.                                                                                                                                              |

a real transmission of the terms of the terms of the

÷ •

Version 7.1, October 1992

# **Customer Support**

Thinking Machines Customer Support encourages customers to report errors in Connection Machine operation and to suggest improvements in our products.

When reporting an error, please provide as much information as possible to help us identify and correct the problem. A code example that failed to execute, a session transcript, the record of a backtrace, or other such information can greatly reduce the time it takes Thinking Machines to respond to the report.

If your site has an applications engineer or a local site coordinator, please contact that person directly for support. Otherwise, please contact Thinking Machines' home office customer support staff:

U.S. Mail:

Thinking Machines Corporation Customer Support 245 First Street Cambridge, Massachusetts 02142–1264

Internet Electronic Mail:

customer-support@think.com

ames!think!customer-support

uucp Electronic Mail:

**Telephone:**

(617) 234–4000 (617) 876–1111

.

# Chapter 1 The Network Interface Chip

The Network Interface chip, or NI, manages the internal communications networks of the CM-5. This chapter presents an overview of the NI's location and function within the CM-5, as well as a description of the features of the NI that are important to you as a programmer.

## 1.1 The CM-5 System: Nodes and Networks

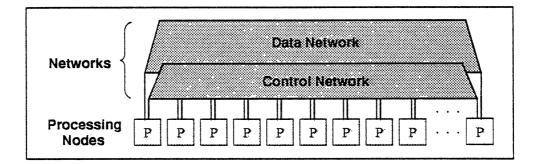

The CM-5 contains a large number of processing nodes linked together by two main internal networks, the *Data Network* and the *Control Network*.

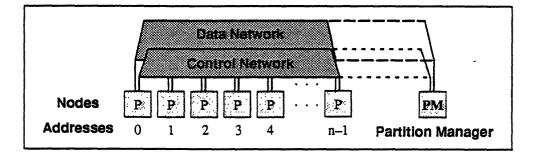

Figure 1. CM-5 processing nodes linked by Data Network and Control Network.

The Data Network is used for high-volume exchange of data between nodes. The Control Network is used to control and synchronize the operations of the nodes.

#### 1.1.1 The CM-5 Networks

The two CM-5 networks are similar to each other in design. Both are scalable high-speed data communications networks. However, the networks are quite different in structure and purpose.

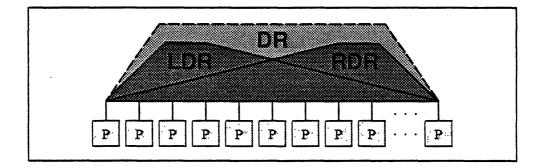

#### The Data Network

The Data Network is a high-speed, high-bandwidth network designed to handle the simultaneous node-to-node transmission of thousands of messages. The Data Network is composed of two halves, the *left interface* and the *right interface*, both of which are connected to all processing nodes. The left and right interfaces can be used either independently or together as the combined *Data Network*.

**Terminology Note:** This combination of the left and right halves of the Data Network is sometimes called the "middle" interface by NI programmers.

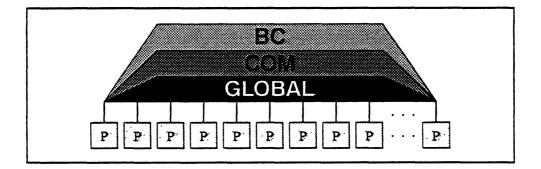

#### The Control Network

The Control Network is used for control tasks that require the joint cooperation of all nodes. It provides three separate functions:

- The broadcast interface distributes a single numeric value to every node. It consists of two subinterfaces: a user broadcast interface and a supervisor broadcast interface.

- The *combine interface* receives a single value from each node, combines the values arithmetically or logically, and then distributes the combined result to all nodes.

- The *global interface* handles global synchronization of the nodes. It consists of a number of distinct interfaces for synchronous and asynchronous messaging by user and supervisor (OS) code.

#### For the Curious: The Diagnostic Network

There is also a third major CM-5 network, the Diagnostic Network, used by the system manager to determine the operational condition of the CM-5 hardware and to diagnose hardware problems. However, because the NI chip is not used to access it, the Diagnostic Network is not discussed further in this manual.

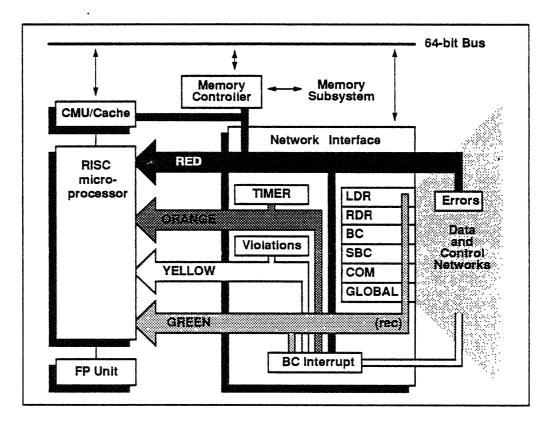

#### 1.1.2 Processing Nodes

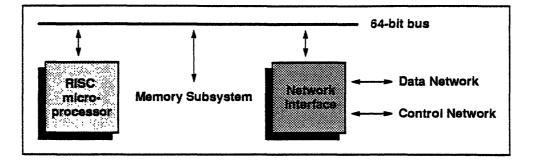

Each processing node contains a RISC microprocessor, a memory subsystem, and a Network Interface (NI) chip, linked together in a bus arrangement:

Figure 2. The components of a typical processing node.

For the Curious: In the current implementation, the microprocessor is a SPARC chip; it executes both user and operating system (OS) code. The memory subsystem consists of up to 32 Mbytes of DRAM memory, controlled either by a single memory controller or by a set of four vector units.

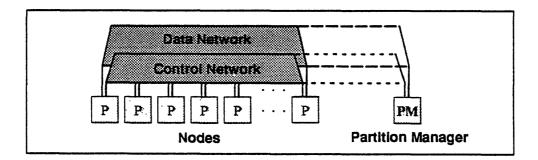

#### 1.1.3 Partitions and Partition Managers

The processing nodes are grouped by software into *partitions*, with each partition monitored by a *partition manager* (PM). (See Figure 3.) Each partition can be as small as 32 nodes, or as large as the entire machine. The partitioning is controlled by the system administrator, who can create and alter partitions as needed.

Figure 3. A partition of nodes and its partition manager.

#### 1.1.4 Programming Models

#### User Programming Model

From a user's point of view, the CM-5 is the single partition of nodes associated with the PM that compiles and executes the user's code. CM-5 user programs compile into two separate sets of code, one for the PM and one for the nodes.

The PM typically controls program flow, and handles all external interactions (communicating with the user by keyboard input and screen output, exchanging files and data with other computing systems over external networks, etc.).

The nodes typically operate in an event-driven loop, waiting for instructions from the PM about which section of code to execute next.

#### **OS Programming Model**

From an OS point of view, the CM-5 is a set of partitions, each of which has a number of associated processes that can be swapped in.

The CM-5 OS manages the execution and swapping of processes within partitions, as well as any exchange of data that takes place between partitions (for example, when a user program needs to read or write data from an I/O device).

Under the CMOST operating system shipped with the CM-5, each PM runs a full and complete UNIX-based operating system, while each of the nodes runs a small kernel of OS code that is optimized for computation and communication. It is this kernel of code that provides the event-driven dispatch loop described in the user programming model above.

#### 1.2 The NI Chip

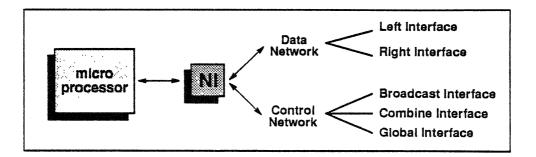

The NI chip serves as an intermediary between the microprocessor and the two CM-5 networks. Each network provides a specific set of *network interfaces*, and the role of the Network Interface chip is to make those interfaces available to the node microprocessor, and thereby to user code and OS code.

Figure 4. NI provides access to features of the Data Network and Control Network.

When the microprocessor directs the NI to send a message via a particular network interface, the NI handles the dispatching of the message, and collects any replies from the networks. The NI uses send and receive FIFOs to hold outgoing messages until they can be sent, and to hold incoming messages until the microprocessor reads them.

The NI chip is register-based; its network functions are controlled entirely by reading and writing NI registers. Access to these registers is provided by memory-mapping — the NI registers are mapped into the microprocessor's memory address space. From a programmer's point of view, therefore, the NI appears as a region of memory with some unique properties.

The microprocessor can either examine the registers of the NI chip to see whether a message has arrived, or it can instruct the NI to signal an interrupt when a message arrives. Interrupts can also be "broadcast" from one NI chip to all other NIs in a partition.

Control of the NI is therefore based on register operations, interrupts, and (in extreme cases) NI Resets, which are described later in this chapter.

## **1.3 The NI Registers**

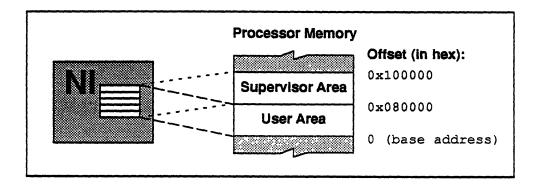

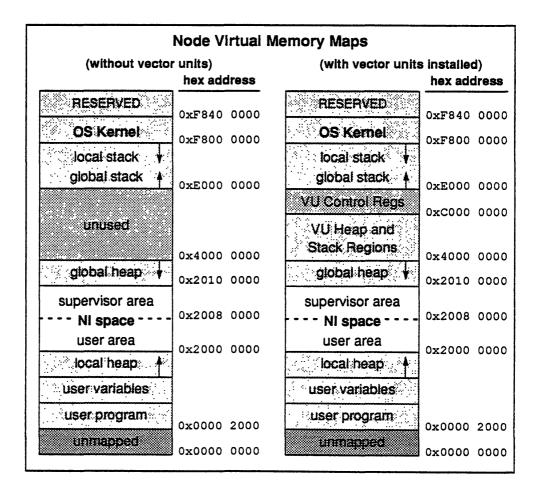

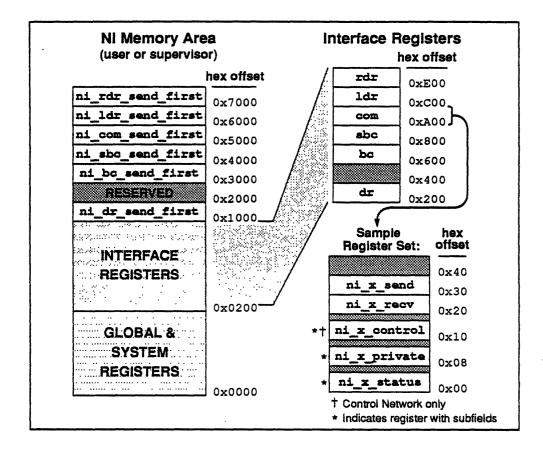

The NI registers occupy a virtual memory region 512 Kbytes long. However, the NI registers are actually mapped into microprocessor memory twice, as two separate virtual memory areas: the *user area* and the *supervisor area*. (See Figure 5.)

Figure 5. The NI registers are mapped into user and supervisor memory areas.

The user area occupies 512K bytes of virtual memory, starting at the base address of the NI memory region (see Section 1.3.4). The supervisor area occupies the 512K bytes immediately following the user area.

The user and supervisor areas contain the same registers at the same offsets, but the hardware mapping is designed so that the NI registers for supervisor features are only accessible from the supervisor area. Any attempt to access supervisor registers from the user area signals a Bus Error. (A programmer sees this as a segmentation violation.) Thus, when this manual speaks of "the supervisor" performing an operation, or of an NI feature that is "restricted to the supervisor," this simply means that only programs with access to the NI supervisor area can perform the described operation or use the described feature.

In general, it is the responsibility of the operating system to make sure that user programs don't have access to the NI supervisor area. Typically, this is done by using virtual address mapping to place the supervisor area in a memory region to which user programs don't have access.

**Note:** Some locations in the NI memory region don't correspond to registers. The effect of reading or writing these locations is not defined, but is never of practical use to programmers. Typically, a Bus Error (see Section 1.4) is signaled.

6

#### 1.3.1 NI Register Types

There are three basic types of NI registers:

FIFO Registers — These "registers" are actually the entry and exit points of send and receive FIFOs associated with the CM-5 networks. Writing a value to a FIFO register pushes that value into the *send FIFO* of the corresponding network. Likewise, reading the value of a FIFO register pops a value from the *receive FIFO* of the network.

Status Registers — These registers are composed of one-bit flags and multibit fields, which indicate the state of the NI and its message FIFOs. For example, most networks have two important status flags, send\_ok and rec\_ok, which indicate the current status of messages being sent or received.

Control Registers — These are status registers containing flags that not only report the state of the NI, but also allow you to control it. Altering the value of a control register's flags has a corresponding effect on the state of the NI. For example, each of the Control interfaces has one or more *abstain* flags that control whether or not the NI participates in the transactions of the network.

**Important:** Some registers are less than 32 bits long, even though they occupy a 32-bit memory location. When such a register is read, the value of the unused bits is undefined. However, when writing to the register, the unused bits should be written with either the same value that was last read from them, or with zeros. The effect of failing to follow this restriction is not defined, but in some cases serious failures can result. (In at least one case, failing to zero out the unused bits causes your partition of nodes to crash. See Section 7.3.1.)

#### 1.3.2 NI Register and Field Names

In this manual, the names of NI registers and register fields are given in the form:

#### ni\_interface\_purpose

The *interface* part of the name identifies the network interface, and is typically one of the following abbreviations:

| dr  | Data Network (left and right) | bc     | broadcast interface |

|-----|-------------------------------|--------|---------------------|

| ldr | left interface                | com    | combine interface   |

| rdr | right interface               | global | global interface    |

The *purpose* describes the purpose of the register or field. Some common examples are:

| send    | Register used to send a network message.              |

|---------|-------------------------------------------------------|

| IGCA    | Register used to receieve a message.                  |

| send_ok | Flag indicating that a message was sent successfully. |

| rec_ok  | Flag indicating that a message has been received.     |

For conciseness, this manual sometimes refers to a register or field by its *purpose* alone. However, this is done only when the intended reference is unambiguous.

The appendixes of this manual include a memory map and a series of lists that exactly specify each register's location and the position and length of any subfields it may have.

#### **1.3.3 NI Register and Field Programming Constants**

There are a number of predefined programming constants that you can use to refer to NI registers and fields in your code.

These constants are defined in such a way that they can be used for both user and supervisor code; the names of the register and field constants are the same for both the user and supervisor areas, and are typically based on the names of the registers and fields themselves.

To get access to these predefined constants, include the header file cmna.h:

#include <cm/cmna.h>

Note: Assembly-language coders may wish to load a more specific file of constants. See the discussion of the CMNA header files in Appendix F.

#### Finding the Constant You Need

Appendix B of this manual lists the names of the NI registers, fields, and flags, and gives the corresponding constants to use in accessing them. Appendix C provides a complete list of the available low-level register and field constants. The types of predefined constants are described below.

#### **Register Constants**

The constants for registers specify the actual address of the register, and there is one such constant for each NI register. To get the name of the constant that corresponds to a register, uppercase the name of the register, and add the suffix "\_A". For example, the constant for the register ni\_dr\_status is NI\_DR\_STATUS\_A.

Note for C Programmers: The register constants are unsigned pointer values. To use them in C code, you must cast them to type (unsigned \*):

```

unsigned *ni_dr_status = ((unsigned *) NI_DR_STATUS);

```

If you don't perform this casting step, the C compiler by default treats the constants as integers, causing warnings about "illegal pointer operations."

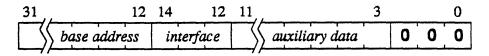

#### **Field Constants**